SiTime在MEMS(微机电系统)技术、模拟CMOS电路设计和开发方面具有深厚的技术专长,并具有成本效益的组装和测试。这些专业技术的结合,都是在SiTime内部进行的,在计时行业中是独一无二的,推动创新的速度要比quartz快得多。除了MEMS和模拟电路的专业知识外,SiTime还具备以优异的质量和可靠性交付大量产品的能力。这种能力来自于我们的装配、测试和校准技术,使我们能够提供一个完全集成的解决方案,完全可以与行业标准的脚印相兼容。

SiTime的基于内存的硅计时解决方案受益于广泛的应用。作为石英设备的替代品,SiTime的振荡器和时钟发生器已经成功地将石英计时工业转化为硅基产品。通过一个全新的全硅平台,SiTime有着卓越的历史成就。我们快速的技术突破是通过利用硅技术的优势,结合了数十年的MEMS谐振器经验和内部模拟技术来实现的。半导体公司正在将我们的硅MEMS谐振器集成到他们的足球/asics中,从而完全消除外部时钟,简化系统设计。

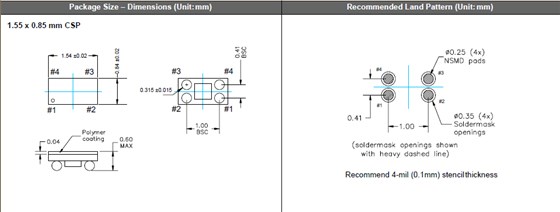

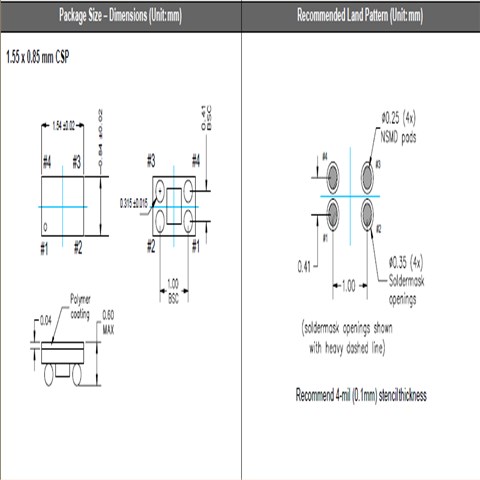

SiTime晶振,32.768K有源晶振,SiT1532晶振.是全球最小,功耗最低的32.768kHz振荡器,针对移动和其他电池供电应用而优化。SiTime的硅MEMS技术实现了最小尺寸和芯片级封装。与现有的2.0*1.2mm SMD XTAL封装相比,该器件可将32 kHz占用空间减少85%。与XTAL不同,SiT1532振荡器输出实现了更大的元件贴装灵活性,并消除了外部负载电容,从而节省了额外的元件数量和电路板空间。

SiTime晶振的真空封装技术:是指石英晶振在真空封装区域内进行封装。1.防止外界气体进入组件体内受到污染和增加应力的产生;2.使晶振组件在真空下电阻减小;3.气密性高。此技术为研发及生产超小型、超薄型石英晶振必须攻克的关键技术之一。

|

SiTime晶振 |

标示 |

SiT1532晶振 |

晶振基本信息对照表 |

|

标准范围 |

f0 |

32.768KHz |

|

|

電源電圧 |

Vcc |

+1.5V~3.63V |

|

|

输出电流 |

Icc |

3.5 mA max. |

Vcc=3.3V |

|

频率负载 |

L_CMOS |

15pF |

LVCMOS出力 |

|

标准频率偏差 |

f_tol |

±10、±20×10-6 max.

|

初期偏差、 |

|

输出电压 |

V |

VOH:Vcc×90% min.VOL:Vcc×10% max. |

|

|

对称 |

SYM |

40%~60% |

50% Vcc |

|

标准时间 |

tr/tf |

12 ns max.(1.8~80MHz) |

10%Vcc~90%、L_CMOS=15pF |

噪音

在电源或输入端上施加执行级别(过高)的不相干(外部的)噪音,可能导致会引发功能失常或击穿的闭门或杂散现象。

电源线路

电源的线路阻抗应尽可能低。

输出负载

建议将输出负载安装在尽可能靠近石英振荡器的地方(在20 mm范围之间)。

未用输入终端的处理

未用针脚可能会引起噪声响应,从而导致非正常工作。同时,当P通道和N通道都处于打开时,电源功率消耗也会增加;因此,请将未用输入终端连接到VCC 或GND。

热影响

重复的温度巨大变化可能会降低受损害的有源晶振的产品特性,并导致塑料封装里的线路击穿。必须避免这种情况。

安装方向

进口晶体振荡器的不正确安装会导致故障以及崩溃,因此安装时,请检查安装方向是否正确。

通电

不建议从中间电位和/或极快速通电,否则会导致有源晶体无法产生振荡和/或非正常工作。

设计振荡回路的注意事项

1.驱动能力

驱动能力说明振荡晶体单元所需电功率,其计算公式如下:

驱动能力 (P) = i2_Re

其中i表示经过晶体单元的电流,

Re表示晶体单元的有效电阻,而且 Re=R1(1+Co/CL)2。

2.振荡补偿

除非在振荡电路中提供足够的负极电阻,否则会增加振荡启动时间,或不发生振荡。为避免该情况发生,请在电路设计时提供足够的负极电阻。

3.负载电容

如果振荡电路中负载电容的不同,可能导致振荡频率与设计频率之间产生偏差,如下图所示。电路中的负载电容的近似表达式 CL≒CG × CD / (CG+CD) + CS。

其中CS表示电路的杂散电容。

频率和负载电容特征图器

振荡回路参数设置参考

SiTime晶振,有源晶振,SiT1533晶振

SiTime晶振,有源晶振,SiT1533晶振 RTC晶振,SM33K进口晶振,PLETRONICS晶振,SM3344KE-32.768K,2520有源贴片

RTC晶振,SM33K进口晶振,PLETRONICS晶振,SM3344KE-32.768K,2520有源贴片