IDT以其智能传感器和行业领先的时间组合来处理汽车应用。IDT在德国的全资子公司- IDT欧洲有限公司(前身为ZMD AG)运营其卓越的汽车中心。IDT是为4G、5G和云计算等无线基础设施应用而设计的高性能的领先创新者。解决方案包括行业领先的射频信号链产品,串行RapidIO®,和先进的时机。

IDT积极提高贴片晶振产品和包装,以产生最快、最可靠的设备。然而,由于产品性能往往受到其实现的影响,因此建议仔细考虑影响设备运行温度的因素,以达到最好的效果。IDT的集成电路用于世界各地的通信、计算和消费行业。IDT总部位于加州圣何塞市,在世界各地都设有设计、运营和销售设施。

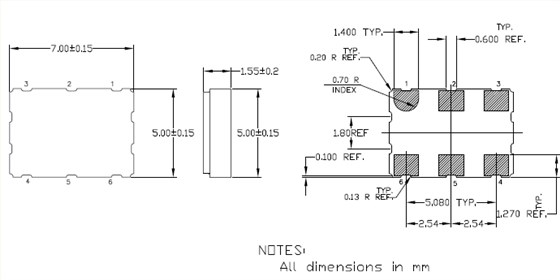

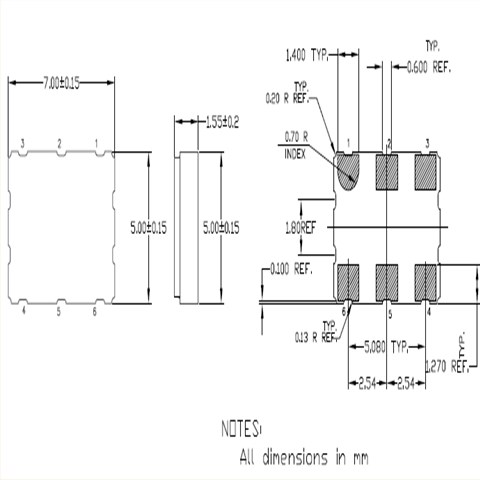

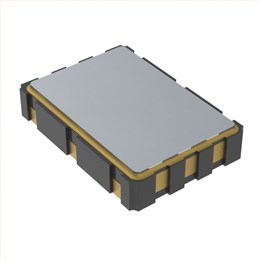

IDT晶振,差分输出晶振,8N4S270晶振.是具有非常灵活的频率编程功能的出厂频率可编程晶体振荡器。该器件采用IDT的第四代FemtoClock®NG技术,以实现高时钟频率和低相位噪声性能。该器件采用2.5V或3.3V电源供电,采用小型,无铅(RoHS 6)6引脚陶瓷5mm x 7mm x 1.55mm封装封装。

该器件可以在工厂编程为15.476MHz至866.67MHz和975MHz至1,300MHz的范围内,并且支持非常高的218Hz或更高的频率精度。扩展的温度范围支持无线基础设施,电信和网络终端设备要求。

|

IDT晶振 |

标示 |

8N4S270晶振 |

晶振基本信息对照表 |

|

标准范围 |

f0 |

15.476MHz~1300.000MHz |

|

|

電源電圧 |

Vcc |

+2.5V、+2.8V、+3.3V |

|

|

输出电流 |

Icc |

3.5 mA max. |

Vcc=3.3V |

|

频率负载 |

L_CMOS |

15pF |

CMOS出力 |

|

标准频率偏差 |

f_tol |

±10×10-6 max.

|

初期偏差、 |

|

输出电压 |

V |

VOH:Vcc×90% min.VOL:Vcc×10% max. |

|

|

对称 |

SYM |

40%~60% |

50% Vcc |

|

标准时间 |

tr/tf |

12 ns max.(1.8~80MHz) |

10%Vcc~90%、L_CMOS=15pF |

操作

请勿用镊子或任何坚硬的工具,夹具直接接触IC的表面。

使用环境(温度和湿度)

请在规定的温度范围内使用耐高温晶振。这个温度涉及本体的和季节变化的温度。在高湿环境下,会由于凝露引起故障。请避免凝露的产生。

晶体单元/谐振器

激励功率

在晶体单元上施加过多驱动力,会导致石英晶振特性受到损害或破坏。电路设计必须能够维持适当的激励功率 (请参阅“激励功率”章节内容)。

负极电阻

除非振荡回路中分配足够多的负极电阻,否则振荡或振荡启动时间可能会增加(请参阅“关于振荡”章节内容)。

负载电容

振荡电路中负载电容的不同,可能导致振荡频率与设计频率之间产生偏差。试图通过强力调整,可能只会导致不正常的振荡。在使用之前,请指明该振动电路的负载电容(请参阅“负载电容”章节内容)。

设计振荡回路的注意事项

1.驱动能力

驱动能力说明振荡晶体单元所需电功率,其计算公式如下:

驱动能力 (P) = i2?Re

其中i表示经过晶体单元的电流,

Re表示晶体单元的有效电阻,而且 Re=R1(1+Co/CL)2。

2.振荡补偿

除非在振荡电路中提供足够的负极电阻,否则会增加振荡启动时间,或不发生振荡。为避免该情况发生,请在电路设计时提供足够的负极电阻。

3. 负载电容

如果振荡电路中负载电容的不同,可能导致振荡频率与设计频率之间产生偏差,如下图所示。电路中的负载电容的近似表达式 CL≒CG × CD / (CG+CD) + CS。

其中CS表示电路的杂散电容。

频率和负载电容特征图器

振荡回路参数设置参考

IDT晶振,差分晶振,8N3D085晶振

IDT晶振,差分晶振,8N3D085晶振 NSC5391B|NDK贴片晶振|汽车应用差分晶振|NP3225SBA有源晶振

NSC5391B|NDK贴片晶振|汽车应用差分晶振|NP3225SBA有源晶振 Silicon品牌,530FB125M000DG,6G网络终端晶振

Silicon品牌,530FB125M000DG,6G网络终端晶振 Silicon品牌,531BB125M000DG,6G差分振荡器

Silicon品牌,531BB125M000DG,6G差分振荡器 Silicon品牌,536FB106M250DG,6G路由器差分晶振

Silicon品牌,536FB106M250DG,6G路由器差分晶振 500DCAA200M000ACH,Silicon品牌,6G路由器差分晶振

500DCAA200M000ACH,Silicon品牌,6G路由器差分晶振 富通晶振,XO53LVDS-167M000-B50A3,5032mm晶振,6G光模块差分晶振

富通晶振,XO53LVDS-167M000-B50A3,5032mm晶振,6G光模块差分晶振 XO75LVD1-312M500-B25B3,Fortiming晶振,6G低功耗差分振荡器

XO75LVD1-312M500-B25B3,Fortiming晶振,6G低功耗差分振荡器 光纤通道晶振,LV3345JEV-125.0MDK,LVDS差分晶振,2520有源晶振,Pletronics振荡器

光纤通道晶振,LV3345JEV-125.0MDK,LVDS差分晶振,2520有源晶振,Pletronics振荡器