终止LVDS与LVPECL晶振阻抗不匹配的3种方法

LVDS和LVPECL都是最常见的差分晶振输出逻辑,可以利用两种相反的信号消除共噪模式,从而达到低相位噪声的设计目的.通常差分输出可以应用到任何一种晶体振荡器身上,市面上常见的LVDS和LVPECL振荡器类型,主要有VCXO,OCXO和SPXO这3种.于ACMOS和低阻抗输出的快速转换,当器件用于驱动阻抗大的阻抗导致阻抗不匹配时,必须使用适当的端接技术.通常用于解决电压反射的问题,这基本上会导致电压反射问题时钟波形以及过冲和下冲的步骤.这种影响可能导致数据的错误时钟,以及更高的EMI和系统噪声.由于PCB走线的长度和负载配置,还需要终止.有三种终止时钟轨迹的通用方法,即将LVDS高精度振荡器的输出阻抗与线路阻抗相匹配的过程:

-系列终端

-上拉/下拉终端

-并联AC终端

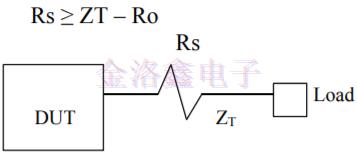

方法1:系列终止

在串联终端中,阻尼电阻靠近时钟信号源放置.Rs的值必须满足以下要求:

大多数Q-Tech晶振都有一个内置串联电阻,典型值介于10Ω和50Ω之间.如果需要额外的电阻,则应将电阻放置在尽可能靠近时钟源的位置.大值电阻可能会增加上升和下降时间,并且与负载和频率有关.

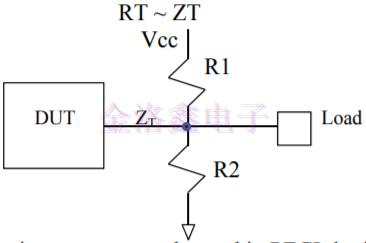

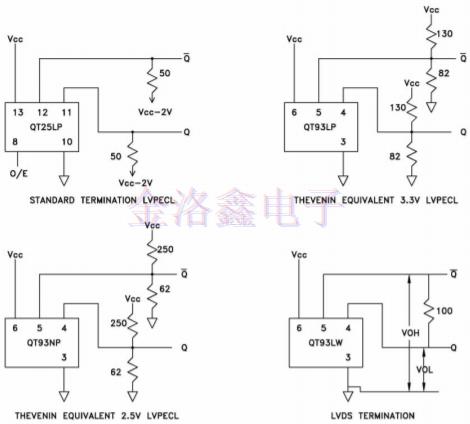

戴维宁终端最常用于PECL逻辑,其负载阻抗为50Ω.

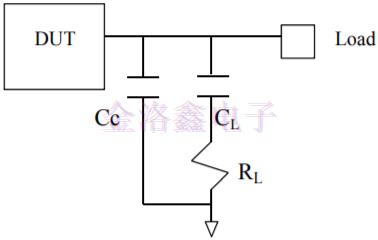

方法3:并行终止

在并联终端中,R-C组合放置在负载处.必须仔细选择电容值,通常小于50pF.建议不要使用此端接,因为它会降低时钟的上升和下降时间,尽管它不会消耗直流电流.

LVPECL和LVDS

LVPECL和LVDS输出晶体振荡器提供了优于HCMOS和TTL技术的优势,具有低成本,高速快速上升和下降时间,低功耗和低抖动.LVDS具有最低的差分摆幅,典型电压摆幅为350mV,典型偏移电压为1.25V以上.

PCB的关键指南

-RF信号对噪声非常敏感.必须小心对待发生和反射的可能性.

-阻抗匹配对RF至关重要.PCB设计人员必须考虑保持线路阻抗为50Ω;驱动器输出50Ω,传输时50Ω,接收器50Ω.

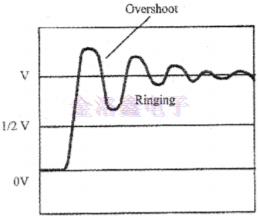

-必须尽量减少回损.这种损失是由信号反射或振铃引起的.返回是返回电流所采用的路径.

由传输线上的阻抗不匹配产生的振铃

-在Vcc和地之间添加去耦电容,并将它们置于石英晶体振荡器的Vcc电源附近.需要去耦电容器以减少可能传输到时钟信号的噪声.

-记住串扰因素.随着系统性能和电路板密度的增加,串扰问题以及如何处理它变得更加重要.串扰是由于互感和并联电容而在相邻导体之间传递能量.

-同时保持信号走线尽可能远.

-线与eah其他线平行的距离应保持最小值.

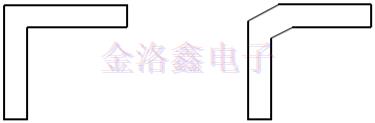

-避免在轨迹上形成90°直角弯曲.除非必要,否则尽量保持笔直,或保持45°切割痕迹.

避免90°直角 弯曲使用45°角弯

LVDS或LVPECL的Q和QNOT之间的差分走线长度应相等,以避免阻抗不匹配和不同的传播延迟时间.

相关常见问题

- Cardinal卡迪纳尔CX532Z-A5B3C5-70-12.0D18晶振常见问题

- 科普6G通信设备晶振重要指标之抖动与相位噪音的基础知识CSX-750FBC25000000T

- 如何通过振荡频率评估石英晶体单元和振荡电路匹配性X1G0002310272

- 温度变化对石英晶体的影响CM200C32768EZFT

- 从组装到最终产品——石英制造过程的最后阶段1C241600CDAA

- 石英生产过程:从石英块到石英坯CX2520DB16000D0GEJCC

- 生产振荡石英晶体用的是真的岩石晶体吗Q-SC32S0321060AAAF

- 石英晶振采购需要特别留心的几个问题和技巧,致广大用户

- 如何看待低频振荡器的输出电平与回波损耗

- 你知道什么时候使用MEMS晶振比较好以及它的价值吗?

手机版

手机版