灵活的晶体振荡器设计可简化时序架构

以往传统的晶体振荡器基本可以满足当时的产品需要,后期随着各种智能型,AI,多功能设备机器的出现,常规的振荡器性能支持不了产品设计要求,需要更灵活的晶振方案.什么是灵活性石英晶体振荡器呢?说到灵活性的振荡器,大家首先想到的应该是MEMS可编程晶体振荡器了吧,因为它具有频率可编程功能,可以任意选择任何一种频点进行编程,简化时序架构.

由于现代电子系统所需参考时钟的频率和抖动要求差异很大,因此通常需要各种独立的晶体振荡器和固定频率时钟乘法器IC,以为数据路径和控制平面提供完整的时序架构..Si5338是业界第一款时钟发生器,能够在四个独立的输出时钟上支持任何速率的频率合成.通过提供这种水平的频率灵活性,Si5338消除了对固定频率时钟发生器和分立石英振荡器需求.

现代通信,网络和广播视频硬件设计使用各种各样的处理器,FPGA,存储器和物理层收发器来执行最终应用程序所需的所有任务和过程.由于新设计中集成度的不断提高,这些应用中的时序架构变得越来越复杂.每个IC都有其自己独特的参考时钟要求,必须在单个设计中仔细管理多个时钟域.进一步复杂的硬件设计,带有嵌入式串行器/解串器(SERDES)的高速物理层收发器和FPGA具有严格的抖动要求,以确保符合最终应用的误码率(BER)规范.表1列出了流行的通信,网络和广播视频应用中处理器,存储器和物理层收发器所需的各种典型时钟频率.

|

零件 |

典型参考时钟(MHz) |

|

处理器/网络处理器 |

33.33、66.66、100、125、133.33 |

|

记忆 |

100、133、166、200、266 |

|

快速以太网 |

25 |

|

千兆以太网 |

125 |

|

光纤通道 |

106.25 |

|

PCIExpress2.0 |

100 |

|

的xDSL |

35.328、70.656 |

|

SONET/SDHOC-3/STM-1 |

77.76 |

|

SONET/SDHOC-12/STM-4 |

155.52 |

|

HD-SDI |

74.1758,74.25 |

|

3G-SDI |

148.3517、148.5 |

|

T1 |

1.544 |

|

E1 |

2.048 |

表1.典型时钟频率(按应用)

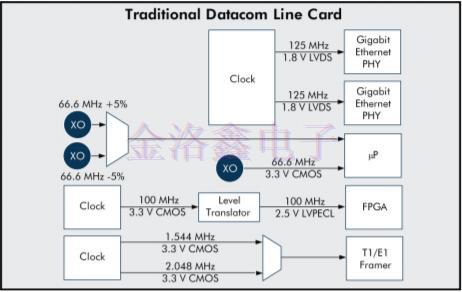

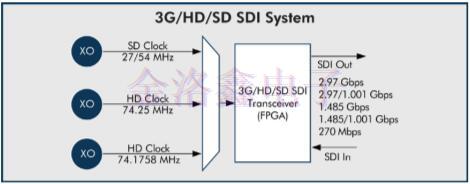

传统时序架构的示例在最终应用中提供了时钟生成和时钟分配,如图1和2所示.

图1.通信和网络应用中的传统时序架构

图2.广播视频应用中的传统时序架构

鉴于每种硬件设计的独特要求,通常使用固定频率时钟发生器/乘法器,离散时钟晶振和复用器的组合为每种应用定制时序架构.当时钟发生器和IC之间需要时钟格式转换时,需要额外的电平转换器IC.某些应用需要多协议高速串行数据传输,如上面图2中的HDTV广播视频示例所示.这些应用需要多个振荡器和支持多路复用器的电路来支持应用的多协议要求.

除了产生标称时钟频率之外,某些应用还需要频率裕度时钟,这些时钟产生的参考电压相对于标称频率略有正或负偏移(例如66.6MHz±5%).这些频率裕度时钟用于产品验证和/或制造测试期间,以测试设计在电压和温度范围内的稳健性,并确保为系统中的关键组件提供足够的设置和保持裕度.传统上,已使用分立的定制频率贴片振荡器来实现频率裕度.由于这些额外的组件仅在产品验证和/或制造测试期间使用,而不是在正常运行期间使用,因此BOM成本和复杂性增加以支持此要求.

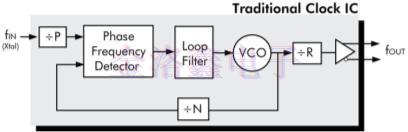

传统时钟倍频器架构:

传统的时钟发生器使用简单的基于整数N锁相环(PLL)的架构.输出时钟频率是输入时钟频率和PLL分频器值的函数,如公式和图3所示:

图3.传统的Integer-NPLL时钟架构

传统的基于PLL的单IC解决方案适用于参考输入的简单整数时钟乘法或晶体输入的时钟生成.但是,许多应用程序要求生成多个非整数相关频率的时钟(例如125MHz以太网和106.25MHz光纤通道).传统解决方案要求更改晶体频率以支持每个独特的频率计划.这迫使设计人员使用一个或多个定制晶体和多个时钟发生器IC来生成所需的一组频率,从而增加了整体解决方案的成本,复杂性和功耗.

新的无速率时钟乘法器架构简化了设计:

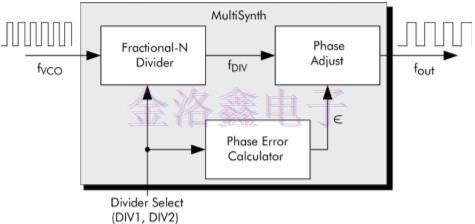

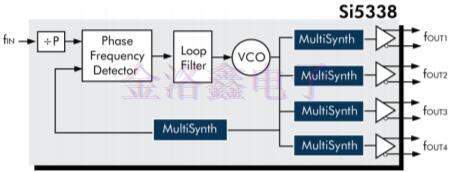

混合信号模拟设计的最新进展使得从单个设备提供任意速率的频率合成成为可能.如图4所示,Silicon晶振公司最新的时钟架构利用分数NPLL与称为MultiSynth的低抖动分数分频器配合使用,以在多个输出时钟上产生任意速率的频率合成.该新产品系列的旗舰产品是Si5338Any-Rate,Any-Output Quad Clock Generator.通过将四个PLL的频率合成功能集成到单个器件中,该技术大大简化了时序架构,与传统解决方案相比,极大地减小了尺寸和功耗要求.

图4.Si5338任意速率、任意输出时钟发生器架构

多重合成技术:

图5显示了多合成器小数分频器的详细框图.Si5338的低相位噪声、高频压控晶振在四条独立输出路径的每一条路径上为MultiSynth模块提供高频输出时钟.多合成器架构的第一级是小数N分频,它可以在两个最接近的整数分频值之间无缝切换,以产生误差为0ppm的精确输出时钟频率.为了消除此过程产生的相位误差,多合成器计算小数N分频产生的时钟和所需输出时钟之间的相对相位差,并动态调整相位以匹配理想时钟波形.这种新颖的方法使得产生任何输出时钟频率而不牺牲抖动性能成为可能.基于这种架构,每个输出时钟可以单独编程,以产生0.16至350MHz的任何频率,并选择频率至700MHz.这种基于多合成器的架构实现的典型抖动性能为1ps均方根值.

图5.多同步架构概述

这种基于多同步的架构提供了出色的抖动性能,如表2所示.

|

参数 |

测试条件 |

最大抖动 |

|

随机相位抖动(12kHz至20MHz) |

|

1.5psRMS |

|

确定性 相位抖动 |

多合成器产生的除数 |

15pspk-pK |

|

多合成器产生整数除数 |

10pspk-pK |

|

|

总抖动 (12kHz至20MHz) |

多合成器产生的除数 |

36pspk-pK |

|

多合成器产生整数除数 |

20pspk-pK |

|

|

周期抖动 |

N=10,000个周期 |

50pspk-pK |

|

周期抖动 |

CLKIN=25MHz 所有CLKns在100MHz |

30pspk-pK |

表2.Si5338任何速率,任何输出ClockGenerator的抖动性能

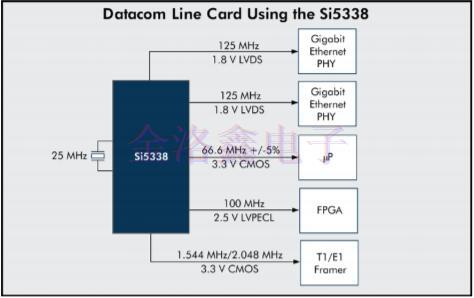

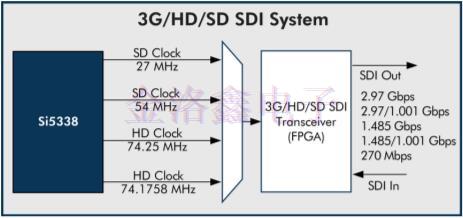

如图6和7所示,这种水平的抖动性能使将数据路径和控制平面时钟整合到单个设备中成为可能.除了显着简化BOM成本和复杂性之外,通过移植可以节省50%或更多的功率.这个新的解决方案.由于将多个组件替换为采用小型4x4mm24-QFN封装的单个IC替代了电路板空间,因此可以将电路板空间最小化.

图6.Si5338简化了通信和网络时序架构

图7.Si5338简化了广播视频时序架构

板级测试的频率裕度:

使用这种方法可以大大简化频率裕度,因为多合成器的分数分频器值可以动态更改,以便时钟输出产生可变的时钟源.所有频率转换都是连续且无干扰的.使用这种架构,可以实现小至1kHz和大至10MHz的频率转换.每个输出时钟的频率都可以在最高350MHz的任何频率下动态更改.结果,可以消除传统上用于板级测试的独立晶体振荡器.

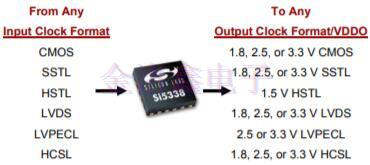

综合水平翻译:

每个Si5338输出时钟的信号格式都可以由用户编程为图8中列出的任何选项.此功能消除了大多数设计中使用外部电平转换器的需要.此外,由于每个Si5338输出时钟都有独立的电源电压,因此简化了在混合电源应用中的使用.每个器件的输出都可以编程为支持下面列出的任何输出时钟/VDD组合.例如,可以同时支持1.8V LVDS,3.3 VCMOS和2.5 VLVPECL.晶振内核由工作在1.8V,2.5V和3.3V的独立电源电压工作,并且与输出时钟电源电压(VDDO0至VDDO3)无关.

图8.Si5338提供用户可编程的输出时钟格式

Si5338是业界第一款时钟发生器,能够在四个独立的输出时钟上支持任何速率的频率合成.通过提供这种水平的频率灵活性,Si5338消除了对固定频率时钟发生器和分立晶体振荡器的需求.该器件具有出色的1psRMS抖动性能,使单个器件即可为物理层收发器以及处理器,网络处理器,FPGA和存储器提供参考时序.由于不再需要处于裕度频率的晶体振荡器,因此大大简化了频率裕度.为了进一步降低BOM成本和复杂性,MEMS时钟晶体振荡器支持用户可编程的输出时钟格式,从而消除了对离散电平转换器的需求.Si5338提供的一流性能和集成度极大地简化了通信和广播视频应用中的时序架构.

手机版

手机版