高速串行链路参考Crystal Oscillator相噪评估

传统的实时示波器已被用于确定串行数据信号中的抖动顺应性.这种分析很简单,因为基于示波器的时间间隔误差(TIE)抖动测量可以观察到类似于实际系统的抖动,实际系统的抖动滤波可以在示波器中执行的软件中进行仿真.另一方面,时钟抖动分析传统上由相位噪声分析仪产生抖动,因为它本身具有较低的仪器本底噪声.由于示波器和相位噪声分析仪不同地观察抖动,因此从两个仪器获得相同的值可能具有挑战性.本文介绍了一种基于相位噪声的方法,该方法提供与示波器得出的TIE抖动类似的值,因此也就是实际系统.

PLL如何观察相位噪声

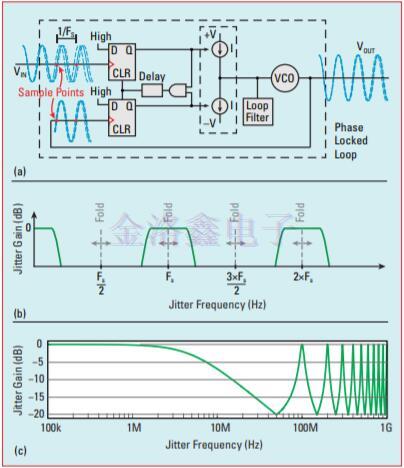

锁相环(PLL)是许多数字和RF系统中的基本构建模块.图1a显示了一个示例PLL,其相位检测器比较相应的输入和反馈边沿,并输出与其相位差成比例的脉冲,然后对其进行滤波以控制VCXO振荡器.在此示例中,相位检测器在其上升沿中点对其输入进行采样.因此,平均采样(FS)和输入时钟频率(FIN)是相等的.

抖动的频谱分量位于奈奎斯特频率(FS/2)以上,或者在采样后折回,低于奈奎斯特频率.图1b说明了PLL抖动传递函数,其低通滤波特性在奈奎斯特频率FS/2的整数倍频谱范围内镜像.在奈奎斯特频率以下,落在PLL环路带宽内的抖动频率无衰减,而落在该带宽之外的抖动频率会因环路的响应而衰减.图1c使用对数x轴绘制具有5MHz闭环带宽的PLL的类似传递函数.该图是任意绘制到1GHz.

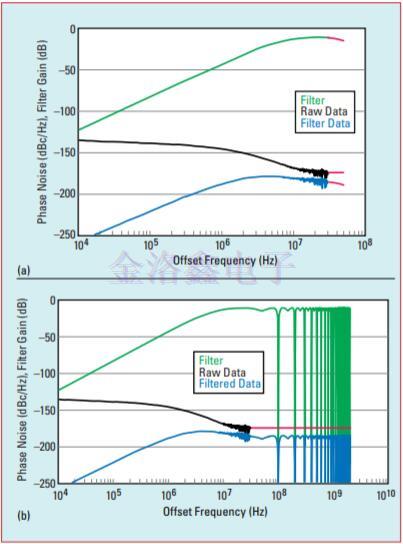

图2说明了100MHz输入时钟信号中的相位噪声如何通过示例PLL2进行滤波,闭环带宽为1MHz.绿色“滤波器”曲线显示PLL的抖动传递函数,最高可达500MHz的任意偏移频率.请注意,x轴表示与载波的频率偏移,适用于相位噪声,因此x轴上的500MHz偏移将出现在信号频谱中的600MHz(例如,500MHz偏移加上100MHz载波).图2显示了100MHz输入信号的相位噪声,使用标记为“原始数据”的黑色曲线.添加滤波器和原始数据曲线会产生蓝色“滤波数据”曲线,表示输入信号的相位噪声通过了多少通过PLL出现在输出信号中.然后,滤波后的相位噪声曲线可以在感兴趣的偏移频率范围内进行积分,以将其转换为抖动.3然而,一些问题使这种积分变得复杂.首先,图2中所示的原始数据曲线无法在高偏移频率下进行测量.相位噪声分析仪直接测量相位噪声,但它只能测量高达基本时钟的一小部分的偏移频率.

图1锁相环(a)说明相位检测器采样的方框图,以及(b)线性和(c)对数x轴的示例抖动传递函数.

图2通过将PLL抖动传递函数(绿色)添加到输入相位噪声原始数据(黑色)以获得输出滤波数据相位噪声(蓝色),在PLL中100MHz输入时钟混叠中的相位噪声示意图.因此,图2中绘制的原始数据曲线仅用于说明.实际上,100MHz时钟信号中的相位噪声只能直接测量,最大偏移频率为30或40MHz,具体取决于仪器.

可以使用频谱分析仪估计较高偏移频率处的相位噪声.然而,由于频谱分析仪无法区分相位和幅度噪声,因此相位噪声的任何频谱分析仪分析都假定相位噪声在所有偏移频率处占主导地位.如果不是这样,则精度会降低,这可能会导致结果乐观或悲观,具体取决于几个因素.4对于石英晶体振荡器,相位噪声通常在接近偏移的频率中占主导地位.幅度噪声和/或调制可能会进一步占据主导地位.

其次,在可以集成滤波后的相位噪声之前,必须确定积分限制.较低的积分限制通常由应用程序设置,例如接收器观察到的抖动传递函数的带宽.上限积分应延长,直到相位噪声降至不显着的水平.可以假设这发生在发送SERDESPLL中的相位检测器块的模拟输入带宽附近.

例如,如果相位检测器的模拟输入带宽是600MHz,则滤波后的相位噪声曲线应该被积分到500MHz偏移(例如,600MHz模拟带宽减去100MHz载波等于500MHz偏移频率).但是,信号的测量相位噪声与其幅度无关,至少在其幅度接近仪器的本底噪声之前.因此,对于第一阶,当信号通过PLL时,输入信号的相位噪声不受相位检测器的模拟输入带宽的影响.

串行数据链接如何观察REFCLK相位噪声

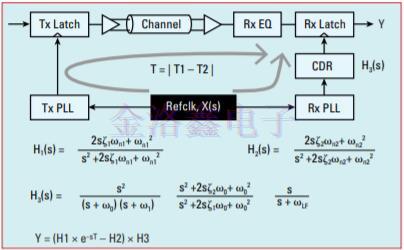

了解PLL采样时输入相位噪声如何混叠,我们现在可以建模串行数据通信链路的抖动传递函数.例如,我们将使用PCIE xpress使用的公共时钟时序架构5-6,如图3所示.这里,refclk相位噪声X由发送PLL抖动传递函数H1和接收PLL和CDR抖动传递函数,分别为H2和H3.请注意,H3是针对图3中的32GT/s链路建模的.整个系统抖动传递函数Y是H1,H2,H3和T的函数,它是发送和接收路径之间的refclk时间延迟.因此,出现在输出数据上的参考时钟晶振的相位噪声贡献被计算为X×Y.

32GT/s的PCIExpress5.0需要使用16种不同的系统抖动传递函数对refclk进行过滤.对于给定的refclk,导致最高抖动的最坏情况函数被计算并绘制在10kHz和30MHz之间,如图4a中的绿色滤波器曲线.原始测量的相位噪声数据也绘制在图4a中,作为标记为原始数据的黑色曲线.最后,通过添加滤波器和原始数据曲线计算滤波后的相位噪声数据,并在图4a中绘制为标记为滤波数据的蓝色曲线.传统的PCI-SIG分析使用实时示波器评估100MHzrefclk中的TIE抖动.

图3PCIe532GT/s系统抖动传递函数(Y)的示意图,用于在公共时钟时序架构中滤波refclk相位噪声(X).示例时钟波形中每个上升沿的TIE抖动,抖动的频谱分量高于50MHz的奈奎斯特频率别名,低于50MHz,如在实际系统中所做的那样.因此,TIE抖动频谱可以扩展到50MHz,并且可以正确地混淆抖动的更高频率成分(如在实际系统中所做的那样).

相比之下,相位噪声分析器包括低通滤波器,其防止晶振测量相位噪声直到偏移频率等于时钟频率的一半(例如,50MHz).因此,通常的行业惯例7是将最后测量的相位噪声数据点扩展到50MHz偏移频率,以匹配TIE抖动频谱的外观.图4a通过使用30至50MHz的红色段扩展三条曲线中的每条曲线来说明这种做法.

问题在于,TIE抖动频谱包括抖动的混叠分量,而图4a中所示的相位噪声频谱则不包括.为了解释混叠,图4b使用(1)红线将最后测量的原始数据相位噪声数据点扩展到2GHz的任意值,并且(2)通过在位于处的光谱边界处镜像它来扩展绿色滤波器曲线.奈奎斯特频率的整数倍(即50MHz).图4b中所示的滤波相位噪声数据作为标记为滤波数据的蓝色曲线现在考虑到相位噪声的混叠分量,直到2GHz的偏移频率.然后可以对滤波后的相位噪声数据进行积分,将其转换为抖动

在执行此集成时,我们观察到低于100kHz的滤波相位噪声足够低,可以忽略.然而,2GHz左右的滤波相位噪声非常重要,事实上,它在积分中占主导地位.结果与上面的PLL分析类似,我们无法定义一个上积分限制来从滤波后的相位噪声中导出抖动.需要进一步分析.

目标

我们的目标是找到一种从相位噪声中导出抖动的方法,该方法与传统上用示波器测量的TIE抖动相匹配(没有从测试环境中添加抖动).由于示波器观察到类似于实际系统的抖动,我们将其结果视为可以判断其他方法的黄金标准(假设示波器不会增加大量抖动,或者可以在后期处理中减去它).本文的其余部分介绍了详尽研究8-9确定这种方法的结论3.该研究分析了由四家不同公司制造的九种不同的时钟设备.

图4(a)不考虑的相位噪声扩展示例,以及(b)在PLL采样时考虑相位噪声混叠.选择恒温晶振器件来覆盖各种抖动值,跨越两个数量级0.1

实证分析

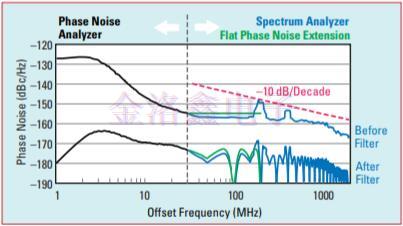

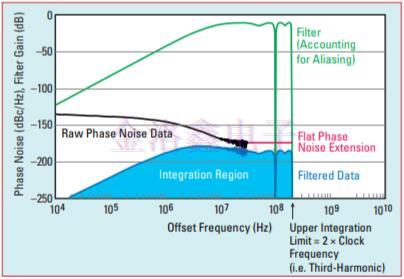

根据经验,我们确定相位噪声分析仪和基于示波器的抖动测量之间的最佳匹配发生在相位噪声分析仪数据作为平坦线延伸到三次谐波时,并如上所述进行后处理.图5显示了在应用系统抖动滤波器之前和之后使用相位噪声分析仪(黑色曲线)测量的100MHz时钟信号.

还绘制了该数据的平坦绿色扩展,直到200MHz偏移频率(例如,300MHz信号频率或三次谐波).作为参考,频谱分析仪数据以蓝色显示.如果我们假设频谱分析仪数据代表相位噪声,则可以通过在曲线上方绘制-10dB/十倍线并将其降低直至与曲线相交来定位主导频谱分析仪相位噪声积分的区域.交叉点识别对该积分或抖动值的主要贡献.观察到该交叉点发生在图5中的三次谐波处.相位噪声频谱明显高于三次谐波,可以安全地忽略.低于三次谐波时,(绿色)平坦相位噪声扩展部分高估并部分低估了信号中的真实相位噪声,相互平衡.由此产生的滤波相位噪声具有平坦的扩展直至三次谐波,可以很好地匹配传统的示波器抖动结果.

图5示例100MHz石英晶振相位噪声,其中位于相位噪声分析仪测量数据(例如,30MHz)之外的积分相位噪声由三次谐波贡献(例如,在200MHz偏移频率)支配.

相位噪声方法论

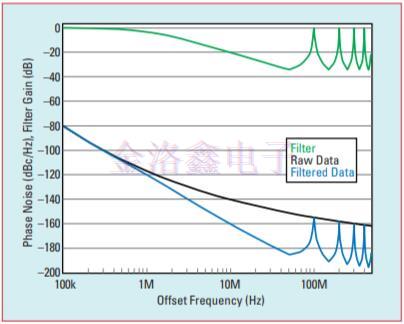

用于分析采样系统中的相位噪声的推荐方法可以总结如下,参考图6.

1.使用相位噪声分析仪(不是频谱分析仪)以dBc/Hz为单位测量DUT的原始相位噪声.图6中示出了100MHz信号.

2.如果需要,删除杂散以仅分析随机噪声.

3.用直线将相位噪声曲线扩展到时钟频率的两倍(即200MHz偏移频率,相当于信号频谱中的三次谐波或300MHz).

4.将抖动滤波器镜像在位于奈奎斯特频率(例如,50MHz)的整数倍的频谱边界上,高达基本时钟频率的两倍(即,200MHz偏移频率).或者(未示出),别名相位噪声数据(来自步骤3)位于奈奎斯特频率之上,低于奈奎斯特频率.

5.过滤相位噪声数据.

6.通过对滤波后的相位噪声数据进行积分得出RMS抖动值,如图6中标记为“积分区域”的阴影区域所示.

时钟晶体和定时行业通常从相位噪声分析仪测量中获得时钟信号中的抖动.另一方面,高速串行数据通信标准通常使用示波器测量串行数据信号中的抖动.最近数据速率的增加需要较低抖动的参考时钟,到目前为止,基于示波器的测试环境所添加的抖动不能再被忽略.这促使创建基于相位噪声的方法,从而产生从传统示波器方法获得的相同抖动值.

相位噪声方法提供了与基于示波器的抖动结果的最佳匹配.1该方法通过将最后测量的数据点扩展到等于两倍的偏移频率来解释采样系统(例如PLL)中的相位噪声的混叠.基本时钟频率.我们假设这种方法提供了与基于示波器的抖动结果的最佳匹配,因为三次谐波处的相位噪声占主导地位.

图6为100MHz时钟推荐的相位噪声方法的总结,它在平均相位噪声扩展时间上加上2倍的时钟频率,然后进行滤波和积分以得出抖动.3计算抖动时的积分,超出此范围相位噪声频谱下降到微不足道的水平.总之,这里介绍的相位噪声方法比相应的示波器方法更快,更简单.由于有源晶振相位噪声分析仪的本底噪声低于示波器,因此在未来的高速串行链路中,时序裕度会缩小,因此该方法也可以更容易扩展.最后,与示波器方法相比,这种方法更适合分析时钟信号,因为相位噪声数据很容易用于精密时钟源.

手机版

手机版