FCD-Tech石英晶体F2520A-30-50-K-30-F-34.000MHz术语和定义理论

晶体单位术语和定义:等效电路,操作方式,并联电容,频率-温度特性,校准公差,稳定性,总频率容差,老化,可拉性,泛音晶体,虚假响应,驱动电平,绝缘电阻,质量指标

晶体单位:术语和定义

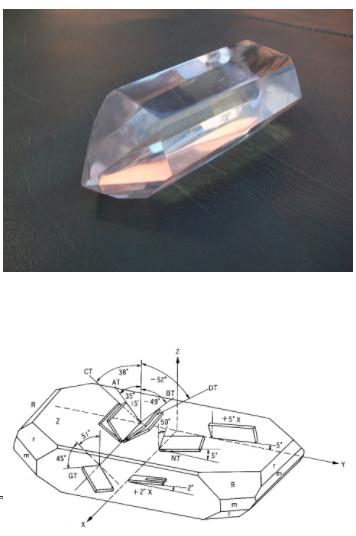

压电效应被定义为施加在石英晶体上的压力产生电压,施加在石英晶体上的电压产生机械振动。这些振动频率由几个因素决定:

●石英晶片的物理尺寸

●相对于石英晶轴的平面或切面

●环境温度

●操作电路

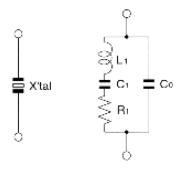

1)等效电路虽然这种压电效应的理论分析是一个相对复杂的机电函数,但可以表示为一个简单的等效电路。

等效晶体电路有助于解释工作在其基本谐振频率附近的石英晶体单元的电特性。由L1、C1和R1组成的串联电路与弹性振动有关,而与串联臂并联的元件Co作为电容归属于石英晶振晶体晶片的电介质。

电阻R1是晶体单元在串联谐振频率下的谐振电阻。(见图1)。

2)操作方式

晶体单元可以用在电路中,以串联或并联两种方式工作。

a)串联谐振:在串联谐振下工作的晶体单元在电路中呈现电阻性,晶体单元的值几乎等于动生电阻R1。大多数晶体都是在串联谐振下制造的,除非规定了负载能力。

b)并联谐振:在并联谐振下工作的晶体在电路中出现电感。晶体频率将由晶体的等效电参数和负载电容CL决定,负载电容CL是决定晶体单元在振荡器电路中使用时的“条件”的一个因素。在普通振荡电路中,晶体单元用在它起感抗作用的范围内。

换句话说,当从晶体单元的两端观察振荡电路时,该振荡电路可以表示为负电阻-R和电容CL的串联电路。那时这个电容叫做负载电容。

负载电容之间的关系小,频率变化量大,并且当负载电容增加时,频率变化降低。如果减小电路中的负载电容,以确保振荡频率有较大的容差,则即使电路中有很小的变化,频率稳定性也会受到很大影响。负载能力可以从数据表上规定的标准值中选择。

3)并联电容

并联电容(Co)是晶振端子之间的电容。它因封装而异,通常在SMD晶振单元中较小,在含铅晶振单元中为6-7pF。

4)频率-温度特性

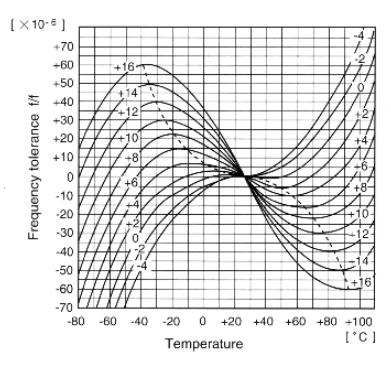

为了将晶体单元用作石英晶体振荡器,要求其振荡频率对温度变化保持稳定。石英晶体具有晶轴,并且晶体切割是根据相对于晶轴的切割角度及其相关的振动模式来定义的。最常用的AT切割晶体单元的频率-温度特性由三次曲线表示。(见图2)以一个角度切割石英晶体晶片,在该角度下,在给定的工作温度范围内获得所需的频率容差。然而,实际上,由于连续工艺中切割和抛光精度的结果,表观切割角可能存在一些差异。因此,需要优化加工精度。

FCD-Tech石英晶体F2520A-30-50-K-30-F-34.000MHz术语和定义理论

5)校准公差校准容差是在特定温度(通常为25°c)下与标称频率的最大容许偏差,通常用百万分率(ppm)或标称频率的百分比来表示。

6)稳定性

稳定性是指在指定温度范围内,相对于标称频率的最大允许偏差,在25°C时以0为基准,用百万分之一或标称频率的百分比来表示。如前所述,该参数取决于贴片石英晶振晶片切割的角度。

7)整体频率容差

总频率容差是指由于温度、时间和其他环境条件的变化,相对于标称频率的最大容许偏差。

8)老化

石英晶体老化适用于频率的累积变化,其导致晶体单元工作频率的永久变化。在运行的前45天,频率的变化速度最快。衰老涉及许多相互关联的因素,一些最常见的因素是:

●内污染

●驾驶水平过高

●晶体表面变化

●各种热效应

●电线疲劳

●摩擦磨损

结合低工作环境、最小驱动电平和静态老化适当电路设计将大大减少老化问题,但不是全部。在10MHz范围内工作的电阻焊接晶体单元的典型老化数字为每年百万分之二(ppm)。

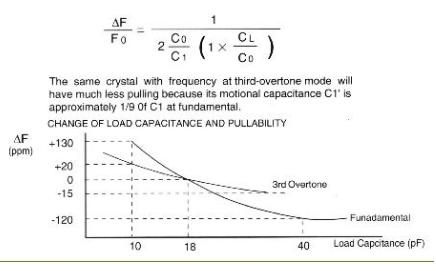

9)可拉性

晶振的可拉性指的是工作在并行模式下的晶振,衡量频率变化与负载电容的关系。对于希望通过改变负载电容值来实现单个晶体多种工作频率的电路设计者来说,可拉性非常重要。

10)泛音晶体该晶体通常在其基频下工作,但通过对电路进行微调,也可以在其3次、5次、7次和9次谐波下工作。泛音晶体经过特殊处理,具有平面平行度和表面光洁度,以增强其在所需泛音谐波振动中的性能。

11)虚假响应

晶体也可能以与其基频或泛音频率无关的频率振动。这种不需要的频率被称为杂散频率。电路设计人员应确保振荡反馈电路在所需工作频率下实现最高增益,从而保护电路免受杂散影响。

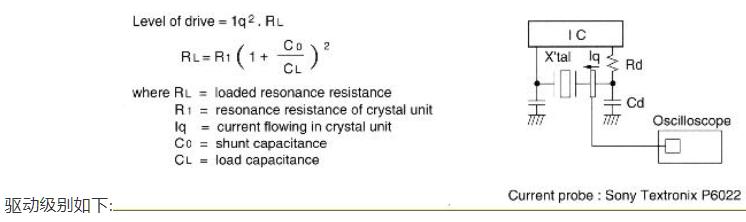

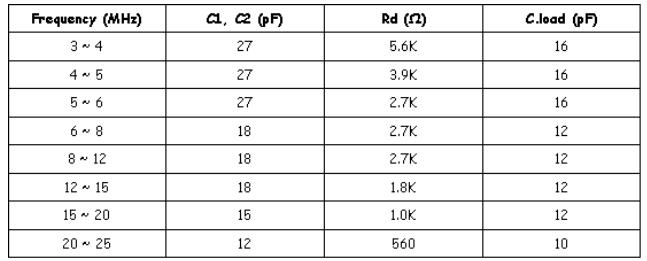

12)驱动级别

由于晶体单元执行机械振动,过多的振动可能导致不稳定的振荡频率,并且最终在最坏的情况下可能导致对石英晶体晶片的严重损坏。设计振荡电路时,应检查驱动电平,以便使用低于数据手册规定电平的石英振荡器。图4示出了确认驱动水平的示例方法。这种方法采用电流探针来测量晶体振荡器电流。在这种情况下,

13)

晶体单元的两个焊接端子之间或引线与外壳(金属外壳)之间的电阻。用100伏15伏的DC电压进行测试,绝缘电阻在500欧姆范围内。

质量因素

品质因数是运动电感、谐振频率和等效串联电阻(ESR)的品质函数。它通常在几万到几十万的范围内。

FCD-Tech石英晶体F2520A-30-50-K-30-F-34.000MHz术语和定义理论

应用笔记:振荡电路

下面介绍由晶体单元组成的典型振荡电路。例如,使用的元素常数。

CL =(c1xc 2)/C1+C2)+杂散电容杂散电容可能从2pF到6pF不等。

1,在C-MOS振荡电路中使用时,电路图中的Rd必不可少,以将驱动电平保持在规定值内并获得稳定的振荡频率。

2,C1和C2应在10 ~ 31pF的范围内使用。如果在30pF以下或以上使用C1和C2,振荡很容易受到电路条件的影响,驱动电平可能会增加或负电阻可能会降低,从而导致振荡不稳定。

3,晶体振荡电路的布局应尽可能短

4,应该减少电路和接地图案之间的杂散电容。

5,应该避免晶体振荡电路图案与其他电路图案交叉。

6,超声波清洗可能会导致晶体单元退化。

FCD-Tech石英晶体F2520A-30-50-K-30-F-34.000MHz术语和定义理论

应用笔记:为微处理器选择晶振除非微处理器数据手册中另有说明,否则本应用笔记可作为选择晶振的一般指南,许多领先的微处理器制造商均可使用该晶振。

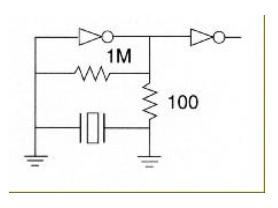

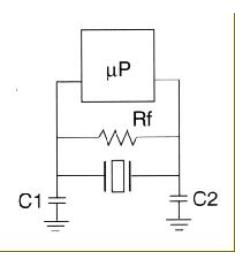

大多数微处理器包括一个带正反馈电阻(典型值为1MO)的反相器设计,该电阻带有一个可选的串联电阻,电阻值从10欧姆到1千欧姆不等(见图A)

它有一个输入端口(通常称为XIN、XI、XTALI或类似性质)和一个输出端口(XOUT、XO、XTALO或类似性质),用于这两个端口之间的晶体单元连接。大多数芯片都设计有一个选项,要么由馈送到晶振输入端口的外部时钟振荡器驱动,要么由外部晶振驱动。

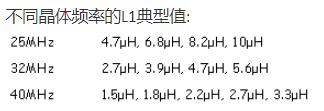

根据共振频率,晶体可以选择基频或泛音模式。通常高于28MHz的频率需要第三泛音模式,以获得价格优势和交付。

在并联模式下,晶体电抗是电感性的,需要两个外部电容(C1)和(C2)来实现振荡中必要的相移。无论晶体是基音模式还是泛音模式,都需要C1和C2。C1和C2的值由芯片制造商指定,从6pF到47pF不等。

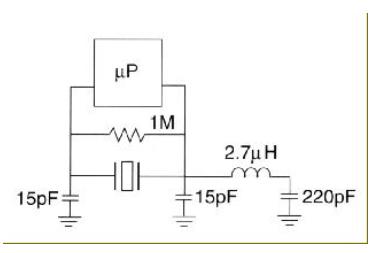

C1和C2可能不均衡,即价值相等,但有时会以特定比率(C1/C2)偏移以获得最佳性能,具体取决于晶体和放大器特性以及电路板布局。图B显示了基本模式操作的典型配置。

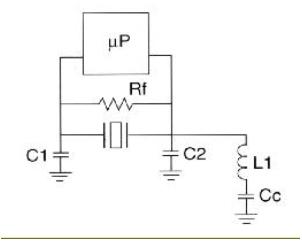

在泛音模式下,需要一个额外的电感L1和电容Cc来选择三次泛音模式,同时抑制或拒绝基音模式。选择第三泛音晶体电路中的L1和Cc值以满足以下条件。串联谐振电路中频率低于基频的L1、Cc分量,使电路在基频时看起来具有电感性。这种情况不利于基模振荡。

并联谐振电路中的L1、Cc和C2分量,频率大约在基频和第三泛音频率的中间。这种情况使电路在第三泛音频率下呈容性,有利于在所需泛音模式下振荡。(见图C)在标准泛音模式下,C2值从10pF到30pF不等。Cc值应至少是C2值的10倍,因此其等效C-equiv。大约等于这个值。

图D显示了40.320MHz三次泛音模式操作的典型电路配置。

FCD-Tech石英晶体F2520A-30-50-K-30-F-34.000MHz术语和定义理论

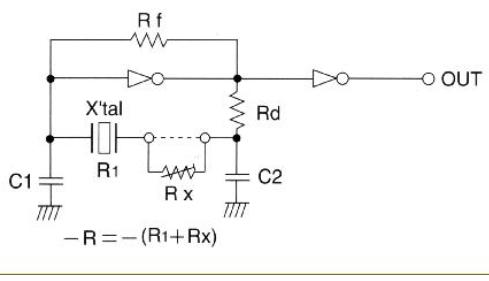

应用笔记:负电阻测量当晶体单元作为振荡电路中的感性电抗被激活时,晶体单元和振荡电路之间的关系如图e所示。为了改善振荡电路的启动条件,最好增加振荡电路的负电阻R参数的值。如果负电阻容差不大(负电阻较小)的电路与具有较大谐振电阻的晶体单元组合在一起,启动条件会变得更糟。振荡电路应设计成负电阻值是谐振电阻的5到10倍。

负载电容的中心值(决定振荡频率的绝对值)和可变范围(振荡频率的微调范围)也必须保持在振荡电路的最佳值。

负电阻测量程序

如图e所示,打开主电路中晶体单元的两端,并在晶体单元中串联一个可变电阻。

改变电阻值,检查当时观察到的振荡极限和电阻(欧姆)。在这种情况下,电源电路必须打开和关闭,不能出错。

电路中的负电阻(-R)是上述数值与晶体谐振电阻R1之和。

这种测量应在工作频率的上限和下限进行

“推荐阅读”

- NDK晶振于智能电表的应用

- 使用TAITIEN的NA/NI-100M-6700解锁新的可能性

- 计时的故事:在古代文明中测量时间

- NDK产品技术更新:NX1612SA

- ECS许多应用需要石英振荡器ECS-100AX-110.5和其他定时解决方案

- 车规级晶体4150AT专用于汽车应用的微晶产品

- Abracon超小型ABS05-32.768KHZ-T音叉晶体专为节能MCU而优化

- Cardinal卡迪纳尔CX532Z-A5B3C5-70-12.0D18晶振常见问题

- Macrobizes主流晶体振荡器SP01-5TK50-A14B-12.288MHz供应

- Bliley压控晶振BVCS5-24.000MHZMDN-ABCBT如何工作?

【责任编辑】:金洛鑫版权所有:http://www.quartzcrystal.cn转载请注明出处

相关技术支持

- FCD-Tech石英晶体F2520A-30-50-K-30-F-34.000MHz术语和定义理论

- ECS许多应用需要石英振荡器ECS-100AX-110.5和其他定时解决方案

- Abracon超小型ABS05-32.768KHZ-T音叉晶体专为节能MCU而优化

- Bliley压控晶振BVCS5-24.000MHZMDN-ABCBT如何工作?

- Microchip用于嵌入式系统的新型PIC18F06Q20微控制器(MCU)

- Golledge下一代GSRFTA0942A频率控制5G网络的解决方案

- CTS最新推出的OCXO完美应用于各个领域

- 遥遥领先的Harmony Electronics Corp.用水晶增强安全驾驶

- 了解遥遥领先的SIWARD希华晶体振荡器

- 领先全球Skyworks晶振为下一代Wi-Fi 6/6E设备提供前所未有的能效

手机版

手机版